Super User

Cyber Trainer

Una piattaforma per la Formazione e l’Addestramento avanzato in ambito Cyber Security

Introduzione

In questo articolo parleremo del progetto Cyber Trainer, che mira alla realizzazione di una piattaforma per la formazione e l’addestramento continui, nel dominio della cyber security, rivolta a figure professionali con livelli di esperienza in ambito alquanto eterogenei. La piattaforma mira a raggiungere questo obiettivo proponendo modalità di formazione e addestramento estremamente innovativi, che includono un blend omogeneo di corsi in e-Learning teorici, corredati di laboratori esperienziali e di apprendimento Sociale, con la possibilità di istanziare scenari complessi e realistici che consentano, ai discenti, di testare sul campo le conoscenze teoriche acquisite in teoria, ed a figure professionali già impiegati nell’ambito, di migliorare ulteriormente le proprie competenze.

CyberTrainer

Guardando all’attuale panorama digitale e a quanto sia divenuto preponderante il ruolo di Internet non solo nella nostra vita quotidiana, ma anche nella nostra economia, possiamo osservare come, se ciò da un lato fornisce una moltitudine di nuove opportunità, dall’altro ci espone ad una nuova serie di minacce e rischi perpetrati da attori con interessi malevoli e criminosi. È pertanto immediato comprendere, sia le motivazioni che si celano dietro il sempre più crescente interesse dell’industria verso le tematiche inerenti alla sicurezza dei Dati e dell’Informazione in generale, sia la conseguente crescita nella domanda di professionisti preparati alla gestione di tali rischi e, soprattutto, che siano costantemente aggiornati, tenendo conto della caratteristica di questo dominio di essere sempre in costante e rapidissima evoluzione.

Ed è proprio per fornire una risposta, valida ed efficace, all’insorgere di questa esigenza che nasce il progetto Cyber Trainer, finanziato dal programma “POR FESR” della Regione Abruzzo, e con l’ambizioso obiettivo di fornire una piattaforma per la formazione e l’addestramento continuo, nel dominio della CyberSecurity. Esso è rivolto ad un pubblico ampio e dalle competenze estremamente eterogenee, in quanto progettato attorno a modelli e paradigmi formativi evoluti e flessibili, che consentono di istanziare facilmente programmi formativi diversificati e specifici per le diverse esigenze.

La piattaforma consentirà ai Docenti di progettare e costruire agevolmente interi percorsi formativi, dalla struttura estremamente flessibile e adattabile alle più svariate esigenze formative, per mezzo dell’aggregazione di Contenuti Formativi eterogenei per tipologia, dimensione e livello tecnico. In questo modo è possibile da un lato, favorire il loro “riuso” inter-percorso e la loro facilità di aggiornamento, dall’altro garantire un apprendimento efficace e mirato ai Discenti, indipendentemente dalla conoscenza pregressa acquisita nell’ambito. A corredo dei corsi appena descritti, definiti di Learning Formale, è stata introdotta un’area dedicata al Social Learning che, grazie anche ad una forte componente di Gamification, consente di coinvolgere in discussioni di approfondimento la community nella sua interezza (Docenti inclusi), favorendo sia il processo di Knowledge and Experience Sharing, sia la volontà, da parte dei discenti, di approfondire argomenti e tematiche in autonomia, per condividerli con la community in piattaforma nella sezione Social, la quale è in grado di ricompensare automaticamente gli utenti che propongono contenuti validi e di interesse.

Dal momento che, nel dominio della cyber security, la previsione di un piano di formazione puramente teorica, che escluda qualsiasi risvolto pratico, è da considerarsi fallimentare già in partenza, Cyber Trainer include una componente “core” predominante, rivolta all’addestramento pratico, di elevata qualità tecnica e tecnologica. L’Area di Addestramento consentirà:

- - ai discenti, che intendono fruire di un percorso formativo teorico, di poter mettere immediatamente in pratica quanto appreso, per mezzo di laboratori esperienziali mirati e specifici, integrati nativamente nei percorsi formativi (sotto forma di veri e propri Contenuti Formativi di tipo esperienziale) e di complessità variabile, via via crescente, al progredire nella propria carriera formativa;

- - ai professionisti del settore, che faranno uso della piattaforma per ricevere aggiornamenti e approfondimenti costanti alle loro conoscenze, di confrontarsi con scenari esperienziali estremamente realistici, di grandi dimensioni. In tali scenari, denominati Cyber Range, i partecipanti organizzati in Team, avranno la possibilità di mettere in gioco le proprie competenze pratiche e conoscenze in ambienti, sì realistici, ma controllati e delimitati, in grado di riprodurre fedelmente problematiche che potrebbero trovarsi ad affrontare in un contesto lavorativo reale.

L’area di Addestramento sarà capace di gestire e tracciare in autonomia i progressi dei discenti attraverso scenari e laboratori, fornendo ai docenti metriche specializzate tramite cui operare miglioramenti ad obiettivi e percorsi formativi. Inoltre è in grado esprimere il suo massimo potenziale quando affiancata all’area denominata di “Test e Rapid Prototyping”, dedicata all’assistenza ai professionisti nella modellazione rapida e nel testing di prototipi innovativi nel dominio della cyber security.

Infine, dal momento che la piattaforma è in grado di esprimere il suo massimo potenziale quando vede lavorare le aree appena descritte in sinergia, l’intero percorso di design e sviluppo della piattaforma è stato incentrato attorno ai seguenti casi d’uso: Operatore SOC, Sicurezza del dominio Automotive, Sicurezza delle Comunicazioni Radio e Sicurezza del dominio IoT.

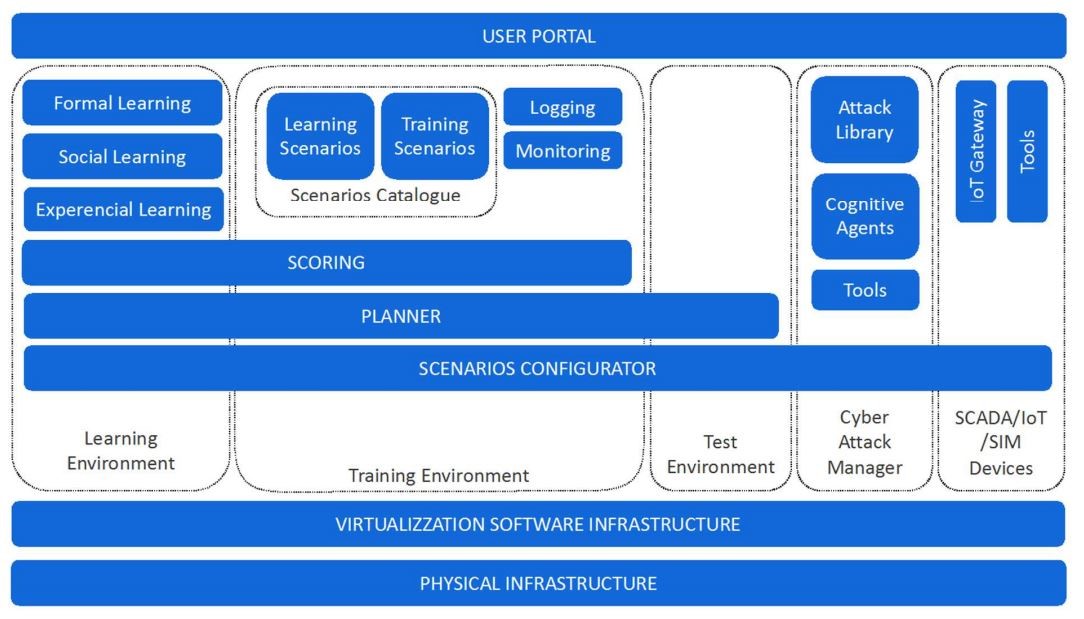

Descrizione architetturale della piattaforma

In questa sezione, con un taglio leggermente più tecnico, verrà presentata l’architettura logica della piattaforma Cyber Trainer e dei moduli principali da cui è costituita.

I blocchi logici principali che ne costituiscono l’architettura sono descritti a seguire:

- - Infrastruttura Fisica: fornisce una pool di risorse a cui la piattaforma può attingere per rispondere alle richieste provenienti dai Discenti, in termini di fruizione di percorsi di formazione e istanziazione di Scenari esperienziali e di test, nel rispetto dei requisiti di performance e scalabilità previsti;

- - Infrastruttura di Virtualizzazione: consente l’avvio e l’esecuzione di scenari di addestramento realistici, garantendo un utilizzo ottimale delle risorse fornite dal livello di Infrastruttura Fisica sottostante;

- - Ambiente di Didattica e Formazione: consente ai Discenti la fruizione di percorsi di formazione personalizzati e adattivi, che aggregano a percorsi e contenuti formativi tradizionali (lezioni, documenti, video, …) una forte componente di Learning Sociale, che abilita la condivisione agevole di conoscenze ed esperienze e aumenta drasticamente le performance di apprendimento andando ad abbattere i tempi e le complessità legate al chiarimento di dubbi o incertezze che possono essere riscontrate nei percorsi teorici.

- - Ambiente di Addestramento: che consente ai discenti tramite il cosiddetto “Hands-on Training” di mettere immediatamente in pratica le conoscenze acquisite, sia su semplici laboratori esperienziali, da eseguire individualmente, che su scenari realistici e complessi, che possono mettere in gioco veri e propri team di professionisti, per confrontarsi con tematiche a approcci metodologici reali. Tutto ciò mentre, in totale autonomia, la piattaforma stessa si occupa di tracciare i progressi ed i traguardi raggiunti dai Discenti attraverso ciascuno scenario di esercitazione.

- - Ambiente di Test e Rapid Prototyping: consente al discente la prototipazione rapida di meccanismi e tool innovativi legati al mondo della Cyber Security e lo supporta nel processo di test degli stessi.

ACACES 2019

Reconfigurable Multiprocessor Systems-on-Chip

Si è svolta a luglio la 15esima edizione della International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES 2019), organizzata da HiPEAC in collaborazione con TETRAMAX Innovation Action e Eurolab4HPC . Come per le edizioni precedenti, Reiss Romoli ha avuto un ruolo chiave nella organizzazione e gestione dell’evento.

Durante la Summer School i partecipanti seguono 4 corsi, scelti tra i 12 del programma, oltre a un Keynote Speach e a un Invited Talk.

A questa edizione hanno partecipato circa 220 ricercatori provenienti da molte delle università europee ed esperti del settore, con docenti provenienti da rinomate università americane e da industrie di punta del settore.

Diana Göhringer ha tenuto il corsodi Adaptive Dynamic Systems al TU Dresden, Germany. Dal 2013 al 2017 è stata assistente professore e capo del MCA (application-specific Multi-Core Architectures) research group alla Ruhr-University Bochum (RUB), Germany.

Reconfigurable Multiprocessor Systems-on-Chip: Hardware Architectures, Design Tools and Runtime Support

The increasing complexity and adaptive dynamic behaviour of cyber-physical systems, such as advanced driver assistance systems (ADAS) or service robotics, require novel embedded hardware/software solutions. In particular, the dynamic behaviour at runtime needs an approach providing adaptation to changing demands in terms of real-time requirements, data throughput, safety and security. One representative example can be found in robotic systems, where changing situations are handled with image processing algorithms for object detection and tracking. Here, besides the change of algorithm, it would also be recommended to change the hardware architecture, e.g. the reconfiguration of accelerators for specific algorithms, in response to changing situations. This feature can be provided by reconfigurable multiprocessor systems-on-chip (MPSoCs), which can adapt the hardware as well as the software to the application requirements and therefore achieve high computational efficiency as well as high flexibility. However, the development, the programming and the operation of such flexible and heterogeneous systems is very complex as the many criteria (performance, power consumption, costs, development time, runtime adaptations, etc.) open a huge design space.

This course is split in three parts. First, basic principles of Multiprocessor Systems-on-Chip including processing elements, communication infrastructure and memory systems are introduced. The second part covers Field Programmable Gate Arrays (FPGAs) and dynamic partial reconfiguration as the basis for reconfigurable computing systems. The third part gives an overview of existing methods and tools for designing and programming such reconfigurable systems and operating system support for managing the runtime adaptations. Throughout the course, several examples of modern reconfigurable systems are presented.

Diana Göhringer, TU Dresden

|

Since April 2017, Diana Göhringer has been professor for adaptive dynamic systems at TU Dresden, Germany. From 2013 to 2017 she was an assistant professor and head of the MCA (application-specific Multi-Core Architectures) research group at the Ruhr-University Bochum (RUB), Germany. She received her PhD and her master degree in Electrical Engineering and Information Technology from the Karlsruhe Institute of Technology (KIT), Germany in 2011 and 2006, respectively. She is author and co-author of over 100 publications in international journals, conferences and workshops. Additionally, she serves as technical programme committee member in several international conferences and workshops. She is reviewer and guest editor of several international journals. Furthermore, she is a member of IEEE, ACM and HIPEAC. Her research interests include Reconfigurable Computing, Multiprocessor Systems-on-Chip (MPSoCs), Networks-on-Chip, Simulators / Virtual Platforms, Hardware-Software-Codesign and Runtime Systems. |

|

ACACES 2019

Technology Entrepreneurship

Si è svolta a luglio la 15esima edizione della International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES 2019), organizzata da HiPEAC in collaborazione con TETRAMAX Innovation Action e Eurolab4HPC . Come per le edizioni precedenti, Reiss Romoli ha avuto un ruolo chiave nella organizzazione e gestione dell’evento.

Durante la Summer School i partecipanti seguono 4 corsi, scelti tra i 12 del programma, oltre a un Keynote Speach e a un Invited Talk.

A questa edizione hanno partecipato circa 220 ricercatori provenienti da molte delle università europee ed esperti del settore, con docenti provenienti da rinomate università americane e da industrie di punta del settore.

Il dott. Bart Clarysse è titolare della cattedra di Entrepreneurship al ETH Zürich dove insegna Technology Entrepreneurship, Lean Start-Up Methods and Technology Commercialization. Ha contribuito alla Summer School con un corso su:

Technology Entrepreneurship

This course gives you an insight into how technologies unfold into commercial activity. Blockchain, the internet of things (IoT), robotics, artificial intelligence (AI), machine learning and so on offer commercial opportunities to found a new venture. However, the potential applications are less clear from a market point of view.

Hence, revenues are not the main focus of these ventures. Novel financing mechanisms such as initial coin offerings (ICOs) and crowdfunding have emerged which provide entrepreneurs with few resources to overcome the lack of revenues.

The challenge which the nascent entrepreneurs face is how to develop a narrative which convinces both financers and co-founders to get off the ground and how to capture the value of what is created.

In complement to these insights, we develop -in teams- practical business cases based upon your own potential business ideas. The focus of these business cases is upon the analysis of the timing of the customer need, the decision as to engage in traditional or novel forms of market research such as design research to test assumptions that are made behind these business ideas versus taking a more experimental route such as the lean startup approach or even engaging in the social mobilization of resources that fit grand societal challenges (e.g. the use of blockchain to install a national crypto-currency).

During these workshops are developed the skills to develop the story of your idea to convince the audience that needs to provide you with the resources to continue.

Bart Clarysse, ETH Zürich

|

Bart Clarysse holds the chair of entrepreneurship at ETH Zürich where he teaches technology entrepreneurship, lean start-up methods and technology commercialization. His research is focused on understanding how nascent industries such as nanotechnology, blockchain, mobile health, IoT unfold over time and which decisions technology entrepreneurs can make to optimize the value capture of their activities or to potentially disrupt existing industry settings. He is also a visiting professor at Imperial College London, where he teaches executive masters in business administration (MBAs) and executive subjects on corporate entrepreneurship and innovation. |

|

ACACES 2019

Memory Systems for the Heterogeneous Era

Si è svolta a luglio la 15esima edizione della International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES 2019), organizzata da HiPEAC in collaborazione con TETRAMAX Innovation Action e Eurolab4HPC . Come per le edizioni precedenti, Reiss Romoli ha avuto un ruolo chiave nella organizzazione e gestione dell’evento.

Durante la Summer School i partecipanti seguono 4 corsi, scelti tra i 12 del programma, oltre a un Keynote Speach e a un Invited Talk.

A questa edizione hanno partecipato circa 220 ricercatori provenienti da molte delle università europee ed esperti del settore, con docenti provenienti da rinomate università americane e da industrie di punta del settore.

Il dott. Aamer Jamel, che è Principal Research Scientist nell’ Architecture Research Group (ARG) di NVIDIA, ha contribuito alla Summer School con un corso su:

Memory Systems for the Heterogeneous Era

Emerging high performance computing systems consist of multiple latency optimized processors (e.g., CPUs) and throughput optimized processors (e.g. GPUs) interconnected using a high performance network.

The performance of such heterogeneous systems is directly dependent on the processor memory hierarchy. This course covers the trade-offs when designing a high performing memory hierarchy for CPUs, GPUs, and heterogeneous systems consisting of multiple CPUs and GPUs.

It has been shown that different design constraints yield different solutions when designing the memory hierarchy. The lectures cover fundamental design concepts and state-of-the-art research in virtual memory, cache hierarchy, and main memory systems.

The course also includes personal experiences on commercializing research ideas and also include discussions topics on areas for continued research.

Aamer Jaleel, NVIDIA

|

Aamer Jaleel is a Principal Research Scientist in the Architecture Research Group (ARG) at NVIDIA. Prior to joining NVIDIA, Dr. Jaleel was a Principal Engineer in the Versatile Systems and Simulation Advanced Development (VSSAD) group in Intel. During his decade-long career at Intel, Dr. Jaleel's research work contributed towards enhancement in performance modelling and cache hierarchy improvements of Intels next generation microprocessors. Dr. Jaleel received his Ph.D. in Electrical Engineering from the University of Maryland, College Park in 2006. He received his B.S. and M.S. in Computer Engineering, also from the University of Maryland, College Park in 2000 and 2002 respectively. Dr. Jaleel has co-authored more than a dozen patents and over 30 technical publications. |

|

ACACES 2019

Distributed memory programming and algorithms

Si è svolta a luglio la 15esima edizione della International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES 2019), organizzata da HiPEAC in collaborazione con TETRAMAX Innovation Action e Eurolab4HPC . Come per le edizioni precedenti, Reiss Romoli ha avuto un ruolo chiave nella organizzazione e gestione dell’evento.

A questa edizione hanno partecipato circa 220 ricercatori provenienti da molte delle università europee ed esperti del settore, con docenti provenienti da rinomate università americane e da industrie di punta del settore.

Durante la Summer School i partecipanti seguono 4 corsi, scelti tra i 12 del programma, oltre a un Keynote Speach e a un Invited Talk.

Nell’edizione 2019 di ACACES il prof. Scott Baden, della University of California, San Diego, ha tenuto un corso su:

Distributed memory programming and algorithms

Distributed memory computers provide bandwidth, processing, and memory scaling capabilities beyond what can be achieved via coherent shared memory. An important consideration in using distributed memory computers effectively is to keep communication costs low, since processing speeds are outpacing communication rates.

Two important models for programming distributed memory are message passing and RMA (Remote Memory Access). RMA comes in many forms, and benefits from global address space communication, that is generally supported by modern network hardware. RMA is employed in PGAS (Partitioned Global Address Space) models which adds global pointers, and optionally, remote procedure call.

These two capabilities play an important role in reducing communication costs, especially for fine grained and irregular communication patterns.

The course has covered message passing and PGAS programming via two libraries, respectively, MPI and UPC++.

The goal of the lectures has been to build a solid grounding in distributed memory programming and the performance trade-offs in efficient implementation.

Algorithmic studies have been presented, and hybrid hierarchical models have been also discussed, which compose distributed memory programming with programming at the node, e.g. multithreading.

The emphasis has been on maintaining low communication costs, as opposed to optimizing computational performance, which is another topic for study.

Scott Baden, Lawrence Berkeley National Laboratory, USA

|

Scott B. Baden is Group Lead of the Computer Languages and System Software Group in the Computational Research Division at Lawrence Berkeley National Laboratory, and Adjunct Professor of Computer Science and Engineering at the University of California, San Diego, where he was a faculty member for 27 years. He earned his Ph.D. from the University of California, Berkeley in 1987. His research interests are in high performance and scientific computation: domain specific translation, abstraction mechanisms, programming models, run times, and irregular problems. |

|

ACACES 2019

Different ways to run a startup

Si è svolta a luglio la 15esima edizione della International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES 2019), organizzata da HiPEAC in collaborazione con TETRAMAX Innovation Action e Eurolab4HPC . Come per le edizioni precedenti, Reiss Romoli ha avuto un ruolo chiave nella organizzazione e gestione dell’evento.

A questa edizione hanno partecipato circa 220 ricercatori provenienti da molte delle università europee ed esperti del settore, con docenti provenienti da rinomate università americane e da industrie di punta del settore.

Durante la Summer School i partecipanti seguono 4 corsi, scelti tra i 12 del programma, oltre a un Keynote Speach e a un Invited Talk.

Per l’edizione 2019 di ACACES l’Invited Talk è stato tenuto dal prof. Erik Hagersten dell’Università di Uppsala, che ha parlato di:

Different ways to run a startup

All startups are different, and there is no magic sauce or formula that will guarantee success. Running a traditional startup is also VERY different from running a successful research project. There are, of course, new areas to understand, such as law, taxes, financing, investors, IP, business planning, validation, prototyping, production, marketing and sales. But not even the most basic areas of the research, such as the baseline systems, simulation methodologies and evaluation principles, may hold for a startup.

The most brilliant research ideas can lead to an unsuccessful startup if all areas are not understood and dealt with appropriately. The talk has been on prof. Hagersten ‘s experience in running two startups: one a more traditional startup that attempted to cover all the areas, and the other a scaled-down attempt to avoid most of the areas.

Erik Hagersten

|

Erik Hagersten has moved between industry and academia about ten times. He holds a professor chair in computer architecture at Uppsala University in Sweden since 1999. Prior to this, he was the chief architect for Sun Microsystem's high-end server engineering division in the US 1994-1999. In 2006 he founded Acumem AB, developing new modeling technology for multicore software optimisations. Acumem was acquired by Rogue Wave Software Inc. in 2010. In 2014 he founded Green Cache AB, developing new and efficient tag-less cache architectures. Green Cache was sold in 2018. At Uppsala, Erik has built up he Uppsala Architecture Research Team, UART (it.uu.se/research/group/uart) – one of the largest architecture research groups in Europe. UART performs research in fast performance modelling technology, compiler technology as well as more traditional computer architecture topics. He is a member of the Royal Swedish Academy of Engineering Sciences (IVA) since 2002. |

|

ACACES 2019

The European Processor Initiative

Si è svolta a luglio la 15esima edizione della International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES 2019), organizzata da HiPEAC in collaborazione con TETRAMAX Innovation Action e Eurolab4HPC . Come per le edizioni precedenti, Reiss Romoli ha avuto un ruolo chiave nella organizzazione e gestione dell’evento.

A questa edizione hanno partecipato circa 220 ricercatori provenienti da molte delle università europee ed esperti del settore, con docenti provenienti da rinomate università americane e da industrie di punta del settore.

Durante la Summer School i partecipanti seguono 4 corsi, scelti tra i 12 del programma, oltre a un Keynote Speach e a un Invited Talk.

Per l’edizione 2019 di ACACES il Keynote Speach è stato tenuto dal prof. Mauro Olivieri, dell’Università La Sapienza di Roma, che ha parlato di:

Roadmap towards exascale: the European Processor Initiative

The historical evolution of supercomputing technologies and of embedded computing technologies exhibits a convergence of targets that narrows the gap between such traditionally distant worlds, and paves the way to an extraordinary future societal scenario.

As a consequence, the sovereignty on power-efficient high-performance microprocessor technology has become a transversal strategic capability for the advancement of modern nations. Europe, after years of delay with respect to other advanced regions of the world, has now started a set of initiatives to gain a new leading position in computing technology.

The first large investment in such direction is represented by the European Processor Initiative, a 4-year 26-partner project whose aim is to design and implement a roadmap for a new family of low-power European processors, for extreme scale computing and a range of emerging applications. The initial core drivers of the development are supercomputing, AI for Big Data, and future Automotive systems.

The opening keynote talk of the HiPEAC ACACES School 2019 has addressed the motivation, objectives, timeline, and technical insights of this unprecedented project, also highlighting the opportunities for further developments.

Mauro Olivieri, Sapienza University of Rome / BSC

|

Mauro Olivieri received the Master (Laurea) degree in electronics engineering and the Doctorate degree in electronics and computer engineering from the University of Genoa, Italy, where he was an assistant professor from 1995 to 1998. In 1998 he joined Sapienza University of Rome as an associate professor, teaching Digital Electronics and Digital Integrated System Architectures. His research interests are digital system-on-chip design, microprocessor core design, and digital nano-scale circuits. He was the scientific responsible for Sapienza University for 2 FP7 ENIAC JU European projects, 1 FP7 IAPP European project, 4 PRIN/FIRB national projects, 11 MIUR University Projects, and 8 industrial research contracts. He was a technical expert for the Italian Economic Development Ministry in the “Smart Specialization Strategy” project on the topic “Smart Cities/Communities”. He is an evaluator for the European Commission in the ECSEL Joint Undertaking. He is a visiting researcher at the Barcelona Supercomputing Center, Spain, within the European Processor Initiative project. He authored over 110 papers and a textbook in three volumes on digital VLSI design. He has been a TPC member of IEEE DATE and was General Co-Chair of IEEE/ACM ISLPED’15. He is a senior member of the IEEE. |

|

DCV683|Overlay Virtual Networking nei data center

DCV690|Introduzione alla Network Automation

Gli ultimi anni sono stati molto proficui per il mondo del networking. Grazie alla sinergia con le tecnologie IT, sempre più integrate nei sistemi di rete, hanno beneficiato della rapidità nell’evoluzione di queste ultime. Esempi sono le tecnologie SDN e NFV nelle loro diverse sfaccettature. Tra le tecnologie mutuate dall’ambito IT, sicuramente la network automation riveste un ruolo molto importante. La lezione appresa dai cloud data center sulla razionalizzazione dei tempi di deployment e di provisioning è stata attuata con profitto nel mondo del networking, portando ad un grande passo avanti nel modo di concepire la gestione degli apparati di rete.

DCV686|Openstack: introduzione ai moduli e all’amministrazione

OpenStack è un insieme di software open source, che consente di realizzare infrastrutture cloud pubbliche o private, altamente scalabili, come ad esempio servizi di cloud storage, compute e networking.

Il corso è incentrato sull’implementazione e la gestione pratica della piattaforma Openstack, e fornisce le competenze per la sua configurazione e gestione. Verrà illustrata la creazione di istanze e dei servizi a supporto di queste (network, dischi virtuali, policy di sicurezza) così come l’amministrazione della piattaforma stessa attraverso la gestione delle utenze, con rispettive quote di utilizzo delle risorse cloud.